cmos平台技术生产是现代半导体制造的核心环节,其发展水平直接决定了芯片的性能、功耗及成本控制能力,作为当前主流的集成电路制造技术,CMOS(互补金属氧化物半导体)平台通过将PMOS和NMOS晶体管集成在同一硅片上,实现了逻辑电路与模拟电路的高效协同,广泛应用于从消费电子到工业控制、人工智能等众多领域,其生产过程融合了材料科学、光刻工艺、薄膜沉积、刻蚀技术及精密控制等多学科尖端技术,是衡量一个国家半导体产业实力的重要标志。

CMOS平台技术生产的核心在于对工艺节点不断微的追求,从早期的微米级发展到如今的7纳米、5纳米甚至更先进节点,每一次节点的缩小都意味着晶体管密度的大幅提升和功耗的显著降低,但也对制造工艺提出了更高要求,在生产过程中,硅片的制备是基础环节,高纯度单晶硅通过拉晶、切割、抛光等工序形成晶圆,其表面平整度直接影响后续光刻的精度,光刻工艺则是将电路图案转移到晶圆上的关键步骤,通过紫外光、极紫外光(EUV)等光源照射,配合光刻胶的曝光与显影,形成微米甚至纳米级的精细图形,随着工艺节点进入7纳米以下,EUV光刻技术的应用成为突破光学衍射极限的必然选择,其光源波长缩短至13.5纳米,能够实现更复杂的图形化处理。

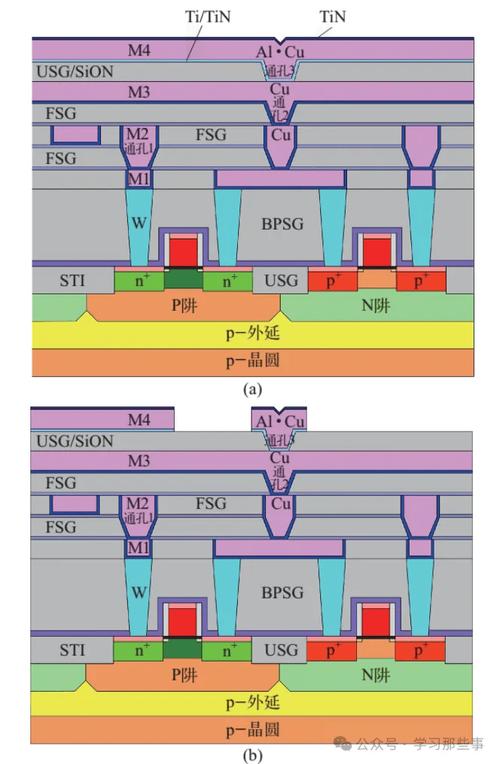

薄膜沉积与刻蚀工艺是构建晶体管结构的核心技术,化学气相沉积(CVD)和物理气相沉积(PVD)技术用于在晶圆表面生长绝缘层、导电层等功能薄膜,其厚度均匀性和致密性直接影响器件性能,而刻蚀技术则通过等离子体或化学反应去除不需要的材料,形成精确的沟槽、通孔等结构,干法刻蚀以其高精度各向异性特点成为主流,能够实现深宽比极高的结构加工,离子注入技术通过向硅片掺杂特定杂质,调控晶体管的导电类型和阈值电压,是形成PN结的核心工艺,化学机械抛光(CMP)技术用于平坦化晶圆表面,确保多层互连的平整度,随着互连层数的增加,CMP的工艺控制难度也呈指数级上升。

在先进CMOS平台生产中,三维集成和先进封装技术的应用日益广泛,通过硅通孔(TSV)技术实现芯片垂直堆叠,大幅提升了集成度和信号传输速度;而扇出型封装(Fan-Out)等工艺则突破了传统封装对尺寸的限制,满足了移动设备对小型化的需求,人工智能与大数据技术的引入正在重塑CMOS生产的质量控制模式,通过实时监测工艺参数、分析缺陷数据,实现了生产过程的智能优化和良率提升,机器学习算法能够预测光刻工艺的偏差,提前调整设备参数,减少废品率。

CMOS平台技术生产的挑战与机遇并存,随着摩尔定律逼近物理极限,新材料(如二维材料、高k介质金属栅)、新架构(如FinFET、GAA晶体管)的不断涌现,为技术突破提供了方向,全球半导体产业链的分工协作也使得CMOS生产更加专业化、规模化,通过建立统一的设计与制造标准,进一步降低了生产成本,加速了技术迭代,CMOS平台技术将继续向更小尺寸、更低功耗、更高集成度方向发展,成为支撑数字经济时代万物互联的核心基石。

相关问答FAQs

-

问:CMOS平台技术生产中的7纳米工艺相比传统28纳米工艺有哪些核心优势?

答:7纳米工艺相比28纳米工艺在晶体管密度上提升约3-4倍,功耗降低约40-60%,性能提升约20-30%,这得益于FinFET晶体管结构的优化、EUV光刻技术的应用以及更精细的互连工艺,使得芯片在相同面积下可集成更多核心,适用于高性能计算、移动终端等对功耗和性能要求严苛的场景。 -

问:CMOS生产过程中,良率控制面临的主要挑战有哪些?

答:良率控制的核心挑战包括:工艺节点缩小导致的缺陷敏感度提升(如纳米级颗粒污染)、设备参数波动对图形均匀性的影响、多层互连的应力控制难题,以及先进光刻工艺中套刻精度(Overlay)的严格要求,生产环境的洁净度(需达到Class 10或更高)、原材料纯度及工艺稳定性也是影响良率的关键因素,需通过实时监控、统计过程控制(SPC)和智能算法持续优化。