SDRAM(Synchronous Dynamic Random Access Memory,同步动态随机存取存储器)是一种广泛应用于计算机、服务器、嵌入式系统等领域的存储技术,其核心特点是数据读写与系统时钟同步,通过时钟信号控制数据传输,相比早期的异步DRAM显著提升了数据传输效率和稳定性,SDRAM的技术标准由JEDEC(固态技术协会)等国际组织制定,涵盖接口规范、时序参数、电气特性、物理封装等多个维度,不同代际的SDRAM标准在性能、容量和功耗等方面不断演进,以满足日益增长的存储需求。

SDRAM技术标准的演进与核心规范

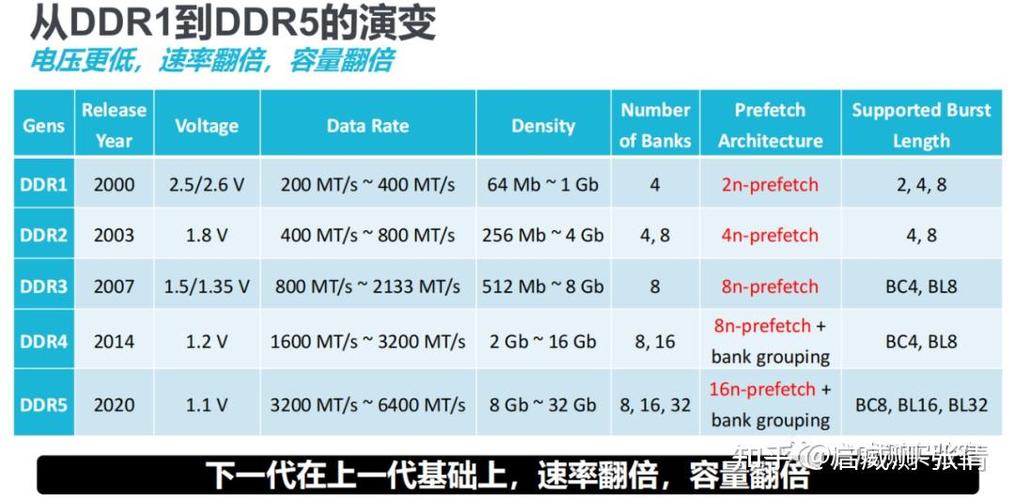

SDRAM的发展经历了从早期标准到现代高速接口的多次迭代,每个代际的标准都针对应用场景优化了架构和协议,以下按代际梳理主要技术标准及其特点:

第一代SDRAM(SDR SDRAM)

SDR SDRAM(Single Data Rate SDRAM)是首个同步动态内存标准,于1993年由JEDEC制定(标准号JESD21-C),其核心特征包括:

- 数据传输速率:单时钟周期传输一次数据,工作频率从66MHz逐步提升到133MHz,带宽可达1.06GB/s(133MHz×64bit/8)。

- 接口与供电:采用3.3V供电,数据总线宽度通常为64bit,地址与控制信号与时钟同步。

- 时序参数:定义了tRAS(行地址到列地址延迟)、tRC(行周期时间)、tRP(行预充电时间)等关键时序,需严格匹配主板芯片组。

- 物理封装:主要采用168-pin DIMM(台式机)或144-pin SO-DIMM(笔记本)封装。

第二代SDRAM(DDR SDRAM)

DDR(Double Data Rate)SDRAM通过在时钟上升沿和下降沿各传输一次数据,实现双倍带宽,JEDEC于2000年发布DDR标准(JESD79),后续升级至DDR2、DDR3:

- DDR SDRAM:工作频率100MHz-200MHz,带宽1.6GB/s-3.2GB/s,2.5V供电,184-pin DIMM封装。

- DDR2 SDRAM:2003年推出(JESD79-2),采用4bit预取架构,频率提升至400MHz-1066MHz,带宽3.2GB/s-8.5GB/s,核心电压降至1.8V,240-pin DIMM封装,支持ODT(On-Die Termination)减少信号反射。

- DDR3 SDRAM:2007年发布(JESD79-3),8bit预取,频率800MHz-2133MHz,带宽6.4GB/s-17GB/s,核心电压1.5V(低功耗版1.35V),支持ZQ校准、数据掩码等功能,240-pin DIMM封装。

- DDR4 SDRAM:2025年标准化(JESD79-4),16bit预取,频率1600MHz-3200MHz(扩展至更高),带宽12.8GB/s-25.6GB/s,核心电压1.2V,288-pin DIMM封装,引入Bank Group架构和Bank Address Multiplexing技术提升并行性。

- DDR5 SDRAM:2025年发布(JESD79-5),32bit预取,频率4800MHz-8400MHz,带宽38.4GB/s-67.2GB/s,核心电压1.1V,采用2个独立32bit通道设计(总计64bit),支持片上电源管理(PMIC)和错误纠正码(ECC)增强。

高性能SDRAM(LPDDR/HBM)

针对移动设备和高端计算场景,衍生出低功耗DDR(LPDDR)和高带宽内存(HBM)标准:

- LPDDR系列:专为移动设备优化,支持更低电压(LPDDR4:1.1V,LPDDR5:1.05V),采用堆叠封装减少空间占用,带宽可达6.4GB/s(LPDDR4)-51.2GB/s(LPDDR5X)。

- HBM系列:通过3D堆叠技术(如TSV硅通孔)实现高带宽,HBM2E带宽达4.8TB/s,适用于AI加速器和GPU,标准由JEDEC和HBM联盟共同制定。

关键技术参数与标准规范

SDRAM的技术标准详细规定了电气特性、时序要求、命令集和测试方法,以下是核心参数的标准化定义:

电气特性

- 工作电压:不同代际SDRAM的核心电压逐步降低,如DDR5为1.1V,以降低功耗。

- 信号电平:采用SSTL(Stub Series Terminated Logic)接口标准,确保信号完整性,例如DDR3使用SSTL18电平(1.8V Vref)。

- 功耗管理:支持多种电源模式(如Active、Standby、Power Down),通过CKE(Clock Enable)信号控制,标准中定义了各模式的切换时序。

时序参数

时序参数是SDRAM性能的关键指标,标准中通过参数组合定义了内存操作的延迟和效率,部分典型参数如下表所示:

| 参数 | 定义 | DDR3典型值 | DDR5典型值 |

|---|---|---|---|

| tCK | 时钟周期时间 | 25ns (800MHz) | 208ns (4800MHz) |

| tRCD | 行地址到列地址延迟 | 9-13tCK | 14-22tCK |

| tRP | 行预充电时间 | 9-13tCK | 14-22tCK |

| tRAS | 行有效时间 | 27-34tCK | 38-56tCK |

| tRC | 行周期时间(tRAS+tRP) | 36-47tCK | 52-78tCK |

| CL | CAS延迟(tAC) | 6-12tCK | 16-32tCK |

| tWR | 写恢复时间 | 6-15tCK | 8-16tCK |

| tRFC | 刷新周期时间 | 160-350tCK | 350-540tCK |

命令集与协议

SDRAM通过命令信号(如RAS、CAS、WE、CS)控制读写、刷新、预充电等操作,标准中定义了命令的真值表和操作时序,DDR5引入了“Bank Group”操作,允许同时激活多个Bank组,提升并行性。

物理规范

- 封装类型:DIMM(台式机/服务器)、SO-DIMM(笔记本)、BGA(移动设备/嵌入式)。

- 层数与布线:DDR5 DIMM采用8层PCB设计,支持信号完整性优化。

- 散热要求:高带宽内存(如DDR5-6000以上)需配备散热片(Heatspreader),标准中规定了热设计功耗(TDP)上限。

标准制定与行业协作

SDRAM技术标准的制定由JEDEC主导,联合三星、海力士、美光、英特尔等企业共同推进,标准制定流程包括:提案征集、技术工作组讨论、草案投票、最终发布,DDR5标准历经3年研发,涉及200多家企业参与,HBM等新兴标准需跨行业协作,如AMD、NVIDIA等GPU厂商参与需求定义。

发展趋势与挑战

未来SDRAM标准将向更高带宽、更低功耗、更先进封装方向发展:

- DDR6:预计2025年推出,目标频率12.8GHz,带宽100GB/s以上,采用32bit预取和更高效的错误纠正机制。

- 内存计算:通过将计算单元与内存集成(如HBM2E with Compute),减少数据搬运延迟。

- 挑战:工艺微缩导致的漏电问题、信号完整性随频率提升的恶化、成本控制等。

相关问答FAQs

Q1:SDRAM与DRAM的主要区别是什么?

A1:SDRAM(同步DRAM)的数据读写操作与系统时钟同步,通过时钟边沿触发数据传输,支持流水线操作,效率更高;而传统DRAM(异步DRAM)的读写由控制信号直接触发,无时钟同步,性能较低,SDRAM支持多Bank并行操作,而异步DRAM通常为单Bank结构。

Q2:为什么DDR5内存需要片上电源管理(PMIC)?

A2:DDR5的工作电压(1.1V)更低,且对电压稳定性要求极高,片上电源管理(PMIC)集成在内存颗粒内部,可实时调节电压和电流,减少主板供电噪声,避免因电压波动导致的信号错误,PMIC支持更精细的功耗控制,提升能效比,满足高性能计算和移动设备的需求。