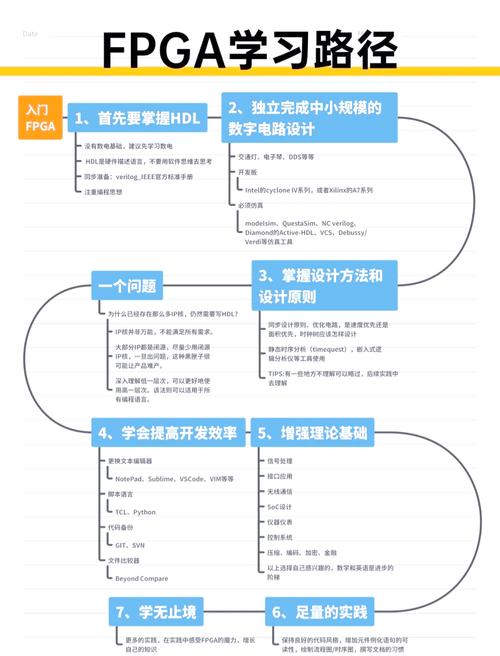

FPGA技术课程设计是电子工程、通信工程、自动化等专业实践教学中的重要环节,旨在通过实际项目开发培养学生的数字系统设计能力、硬件描述语言(HDL)编程能力以及FPGA芯片的综合调试能力,课程设计通常以具体应用场景为导向,要求学生从需求分析、方案设计、代码编写、功能仿真到硬件实现,完整完成一个小型数字系统的开发流程,从而深化对FPGA工作原理的理解,提升工程实践素养。

FPGA技术课程设计的核心内容与实践流程

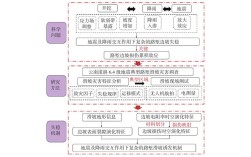

FPGA技术课程设计的核心在于将理论知识转化为实际应用,其流程可分为需求分析、方案设计、代码实现、仿真验证、硬件调试与优化五个阶段。

需求分析与方案设计

首先明确设计目标,例如设计一个简易数字信号处理器、UART通信模块、LED流水灯控制器或小型数字时钟等,根据功能需求,确定系统架构,如数据通路、控制逻辑、接口标准等,设计一个基于FPGA的数字频率计,需明确频率测量范围、分辨率、显示方式等参数,进而选择合适的计数方案(如直接计数法等精度周期法)和显示驱动方式(如数码管或LCD)。

HDL代码编写与模块化设计

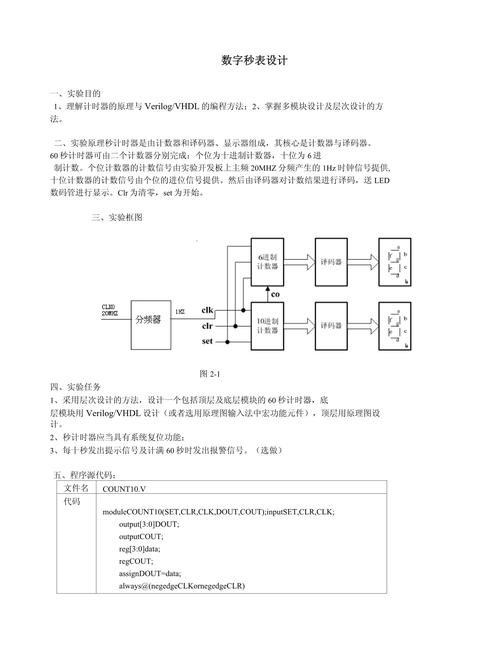

采用Verilog或VHDL等硬件描述语言进行代码开发,遵循模块化设计原则,将系统划分为功能独立的子模块(如分频模块、计数模块、显示模块等),便于调试与复用,以数字时钟为例,可拆分为秒计数模块(60进制)、分计数模块(60进制)、时计数模块(24进制)以及动态扫描显示模块,各模块通过接口信号连接,编写代码时需注意时序规范,避免组合逻辑竞争冒险,例如使用 always 块设计时序逻辑,用 assign 语句设计组合逻辑,并确保敏感列表完整。

功能仿真与逻辑验证

在代码编写完成后,通过仿真工具(如ModelSim、Xilinx ISIM)进行功能仿真,验证逻辑设计的正确性,仿真需覆盖典型输入场景,包括正常工作状态、边界条件(如计数器从59进位到00)和异常情况(如复位信号触发),仿真通过后,进行综合前仿真,检查RTL级代码与逻辑电路的一致性;综合后仿真则验证综合生成的网表与原逻辑的匹配度,确保无功能偏差。

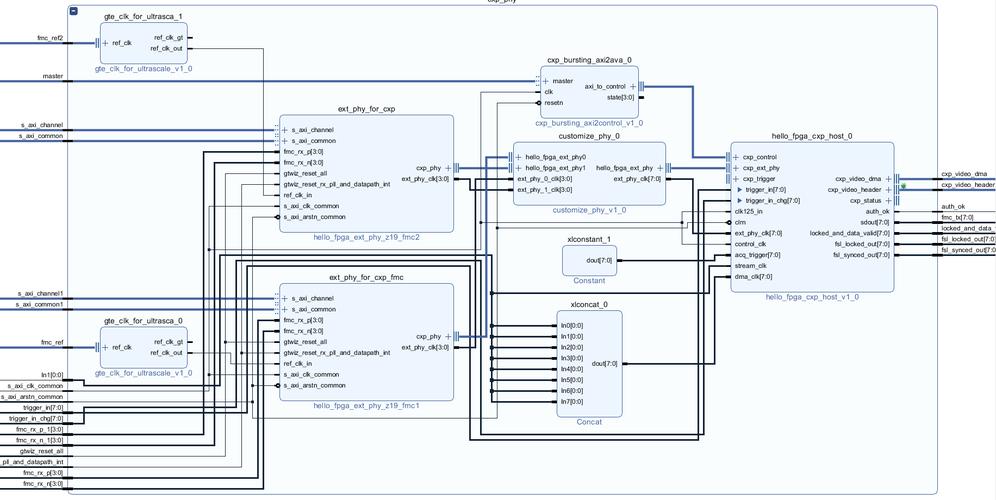

硬件实现与引脚约束

选择合适的FPGA开发平台(如Xilinx Artix-7或Intel Cyclone IV),使用综合工具(如Vivado、Quartus II)将HDL代码转换为门级网表,并进行布局布线,根据开发板硬件资源,编写约束文件(如XDC或UCF文件),定义FPGA引脚与外部设备(如按键、LED、数码管)的对应关系,将时钟信号约束到特定引脚,按键输入信号配置为上拉电阻模式,避免悬空干扰。

板级调试与性能优化

将程序下载到FPGA开发板后,通过示波器、逻辑分析仪或在线逻辑调试工具(如Xilinx ILA)观察实际输出信号,与时序仿真结果对比,定位并修复硬件实现中的问题(如时序不满足、引脚配置错误等),针对资源占用率、功耗、工作频率等指标进行优化,例如通过流水线设计提升系统吞吐量,或优化状态机编码减少资源消耗。

常见设计项目案例参考

| 项目名称 | 核心功能 | 涉及关键技术 |

|---|---|---|

| 数字频率计 | 测量输入信号频率,通过数码管显示结果 | 计数器设计、闸门控制、动态扫描显示、分频电路 |

| UART通信模块 | 实现FPGA与PC之间的串口数据收发,支持自定义数据帧格式 | 异步串口协议、波特率生成、帧同步检测、FIFO缓存 |

| 步进电机控制器 | 通过按键控制步进电机正反转、启停及转速,实现精确定位 | 脉冲生成、细分驱动、方向控制逻辑、按键消抖 |

| 图像边缘检测系统 | 对摄像头输入的灰度图像进行边缘检测(如Sobel算子),并通过HDMI显示结果 | 图像数据处理算法、DDR3缓存控制、HDMI接口时序、并行流水线设计 |

相关问答FAQs

Q1: FPGA课程设计中,如何处理代码综合后的时序不满足问题?

A: 时序不满足通常因关键路径延迟过大导致,可从三方面优化:① 代码层面:拆分组合逻辑长路径,插入流水线寄存器;避免使用复杂的组合逻辑表达式,优先采用状态机或查表法。② 约束层面:合理设置时序约束(如create_clock、set_max_delay),优化布局布线引导工具关键路径布局。③ 资源层面:更换更高性能的FPGA芯片,或降低系统工作频率,确保时序余量(Slack)为正。

Q2: 在FPGA开发板上调试时,发现输出信号与预期不符,如何快速定位问题?

A: 可采用“分层定位法”:① 首先通过在线逻辑分析仪(ILA)抓取关键信号(如时钟、复位、状态机状态),判断顶层模块是否按预期工作;② 若顶层正常,逐级检查子模块输出,例如在计数器模块中观察计数脉冲是否稳定,进位信号是否正确产生;③ 若信号异常,结合示波器检查硬件连接(如引脚配置、上拉/下拉电阻),排除因硬件接触不良或引脚约束错误导致的问题;④ 最后回归仿真,对比硬件实际信号与仿真波形,定位差异点。