FPGA的TDC(Time-to-Digital Converter,时间数字转换器)技术是一种高精度时间测量解决方案,通过将连续的时间信号转换为离散的数字量,广泛应用于激光雷达、粒子物理实验、通信系统等领域,其核心优势在于利用FPGA的灵活性和高速数字逻辑资源,实现皮秒(ps)甚至亚皮秒级别的时间分辨率,同时具备可重构性和低成本特点。

TDC的基本原理是通过计数时钟周期和插值技术来测量时间间隔,在FPGA中实现TDC通常采用三种方法:计数器型TDC、时间-数字转换器型TDC和游标型TDC,计数器型TDC结构简单,通过高频时钟计数实现粗粒度时间测量,但分辨率受限于时钟频率;时间-数字转换器型TDC利用FPGA内部逻辑门传播延迟进行时间-幅度转换,通过比较器或编码器生成数字信号,分辨率可达100ps左右;游标型TDC则通过两级延迟线实现精细时间插值,分辨率可提升至10ps以下,但电路复杂度较高。

FPGA的TDC设计需考虑时钟抖动、温度漂移和工艺偏差等影响因素,为提高测量精度,常采用校准技术,如多相位时钟交叉采样、延迟链校准和温度补偿算法,通过在FPGA内部生成多个相位偏移的时钟,对同一时间事件进行多次采样,可有效减少时钟抖动误差;而利用片上温度传感器实时监测环境变化,并通过查找表调整延迟参数,可补偿温度漂移带来的测量偏差。

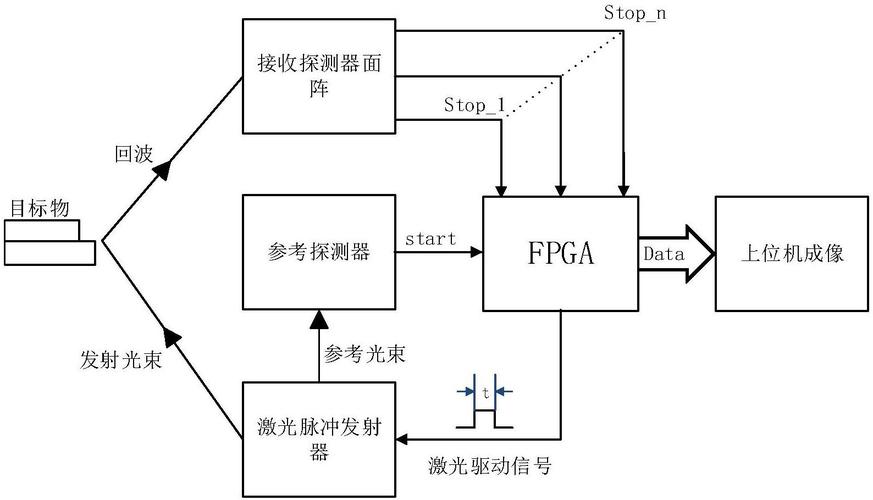

在实际应用中,FPGA的TDC架构可根据需求灵活配置,在激光雷达系统中,TDC可精确测量激光脉冲往返时间,结合光速计算目标距离;在高速通信系统中,TDC用于时钟数据恢复(CDR)和抖动分析;在核物理实验中,TDC则用于粒子飞行时间测量,以下为常见FPGA TDC性能对比:

| 类型 | 分辨率 | 测量范围 | 资源占用 | 适用场景 |

|---|---|---|---|---|

| 计数器型TDC | 1-10ns | μs-ms级 | 低 | 低成本、中精度测量 |

| 时间-数字转换器型TDC | 50-200ps | ns-μs级 | 中 | 通用高精度测量 |

| 游标型TDC | 5-20ps | ns-μs级 | 高 | 超高精度、低抖动需求 |

FPGA的TDC技术还面临功耗和资源优化的挑战,游标型TDC虽精度高,但延迟线和比较器会消耗大量逻辑资源;而计数器型TDC虽资源占用少,但需依赖高频时钟,可能增加功耗,为此,研究者提出混合型TDC架构,结合计数器和插值技术,在精度和资源间取得平衡,采用粗计数+精插值的两级结构,用计数器实现μs级测量,用延迟链实现ps级细化,既保证量程又提升分辨率。

FPGA的并行处理能力可支持多通道TDC设计,通过时分复用或空间复用技术,单个FPGA芯片可集成数十个TDC通道,满足多事件并发测量需求,在粒子探测器中,多通道TDC可同步记录多个粒子的到达时间,通过FPGA的实时数据处理单元进行关联分析,大幅提升系统吞吐量。

相关问答FAQs:

-

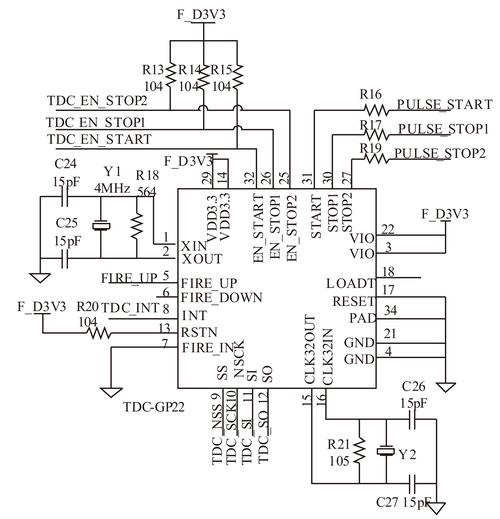

问:FPGA的TDC与专用TDC芯片相比有何优势?

答:FPGA的TDC主要优势在于灵活性和集成度,用户可通过硬件描述语言(HDL)自定义TDC架构,适应不同测量需求;FPGA可集成数据处理、控制逻辑等模块,减少外部电路设计成本,而专用TDC芯片虽性能稳定,但功能固定,难以修改,FPGA的TDC可通过软件升级优化算法,延长产品生命周期。 -

问:如何提高FPGA TDC的抗干扰能力?

答:提高抗干扰能力需从硬件和软件两方面入手,硬件上,采用差分信号传输、电源隔离和屏蔽设计减少噪声耦合;软件上,通过数字滤波算法(如移动平均、卡尔曼滤波)抑制随机误差,在FPGA内部实现时间戳校准,利用参考时钟定期修正测量偏差,可有效降低环境干扰对精度的影响。 (图片来源网络,侵删)

(图片来源网络,侵删)